Ripple carry adder

It is possible to create a logical circuit using multiple full adders to add N -bit numbers. Each full adder inputs a C in , which is the C out of the previous adder. This kind of adder is a ripple carry adder , since each carry bit ”ripples” to the next full adder. Note that the first (and only the first) full adder may be replaced by a half adder.

The layout of ripple carry adder is simple, which allows for fast design time; however, the ripple carry adder is relatively slow, since each full adder must wait for the carry bit to be calculated from the previous full adder. The gate delay can easily be calculated by inspection of the full adder circuit. Each full adder requires three levels of logic. In a 32-bit [ripple carry] adder, there 32 full adders, so the critical path (worst case) delay is 32∗3 = 96 gate delays.

Carry look-ahead adders

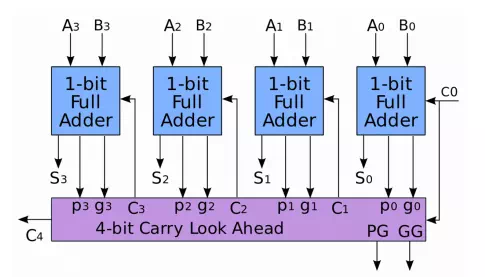

To reduce the computation time, engineers devised faster ways to add two binary numbers by using carry lookahead adder s. They work by creating two signals (P and G ) for each bit position, based on whether a carry is propagated through from a less significant bit position (at least one input is a ’1’), a carry is generated in that bit position (both inputs are ’1’), or if a carry is killed in that bit position (both inputs are ’0’). In most cases, P is simply the sum output of a half-adder and G is the carry output of the same adder. After P and G are generated the carries for every bit position are created. Some advanced carry look ahead architectures are the Manchester carry chain , Brent-Kung adder, and the Kogge-Stone adder.

4-bit adder with Carry Look Ahead

Some other multi-bit adder architectures break the adder into blocks. It is possible to vary the length of these blocks based on the propagation delay of the circuits to optimize computation time. These block-based adders include the carry bypass adder which will determine P and G values for each block rather than each bit, and the carry select adder which pre-generates sum and carry values for either possible carry input to the block.

Other adder designs include the conditional sum adder , carry skip adder, and carry complete adder.

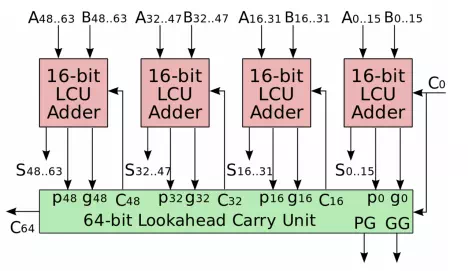

Lookahead Carry Unit

By combining multiple carry look-ahead adders even larger adders can be created. This can be used at multiple levels to make even larger adders. For example, the following adder is a 64-bit adder that uses four 16-bit CLAs with two levels of LCUs.

A 64-bit adder